引言

在反向整流控制中,需要6个控制IGBT的同步信号,在以前的试验中,同步信号的获取是先由模拟电路对两个线电压进行调理,然后两个线电压信号再进入DSP通过AD转换为数字信号进行处理,数字信号处理中又通过锁相环或者带通滤波处理得到正弦同步信号,最后通过这两个正弦信号进行适当的逻辑处理得到6个控制IGBT的同步信号,在这种同步信号的获取中硬件电路需要有DSP或者MCU处理器来处理,涉及到这类信号处理器就要考虑其可靠性,如抗干扰方面、PCB板布局方面、芯片多管脚的焊接方面等。

针对上述情况,乐鱼考虑是否能直接用部分模拟电路简单产生信号,然后通过CPLD进行逻辑处理得到6个同步信号,在单元控制板中,由于逆变也需要利用CPLD来处理逆变部分的信号和与主控进行通信的处理,所以CPLD是必不可少的,因此由模拟电路产生的信号通过CPLD处理也是比较直接的过程。

1、存在的问题

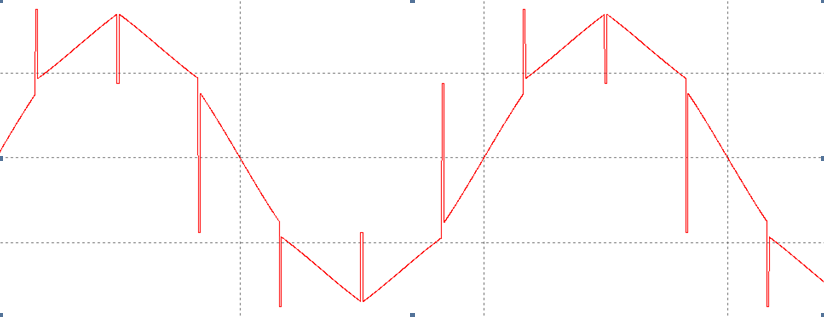

在模拟训练集成运放导致移动信号中,通常更是对线交流电流还相交流电流过零零的拿,在过零零的拿中常常用的是用运放到行过零更。在反方向整流工作的中,随着开关电压的电压表内阻长期出现,在放入开关电压上就长期出现IGBT开通了或关断时导致的拐点,长为1随时:

上图为反向整流工作时的电源相电压,对此如果用线电压获取同步信号时就会存在线电压过零点的不准确,如果对线电压进行滤波处理虽然可以去掉缺口,但可能对信号产生相移,从而用线电压进行比较获取过零点并不大合适;如果用上图相电压进行过零比较来获取过零点,这样在缺口处和过零点处就出现过零点信号,由于缺口处的宽度比较窄,缺口处可以通过CPLD处理去除,然后留下比较真实的过零点,但是由于变压器到单元之间为三相三线制,不存在中线,所以需要通过三相制造一个中点,但这样这个中点的电位是不确定的,是浮动的,所以也完全可能造成过零点不准确,特别是三相出现不平衡时就比较明显,对此采用相电压进行过零比较也是不大合适。

2、解决的方法

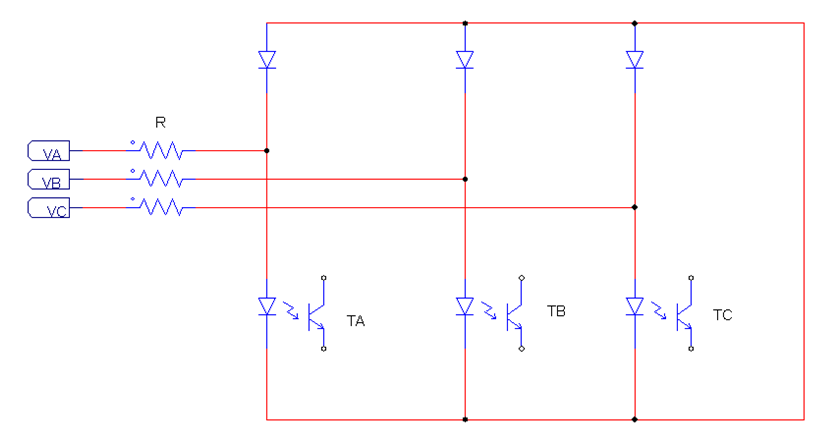

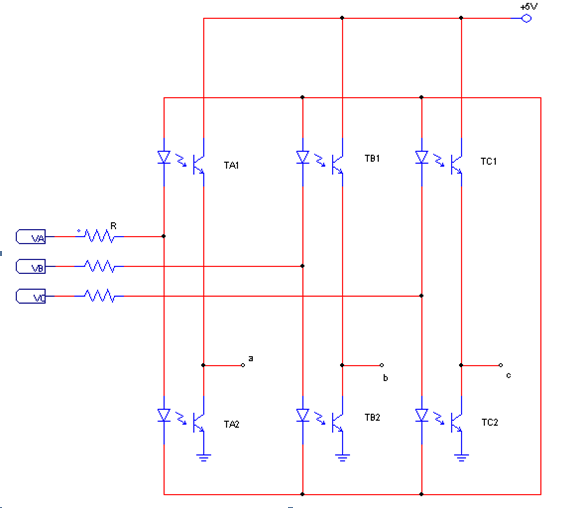

图2、光耦获取同步信号

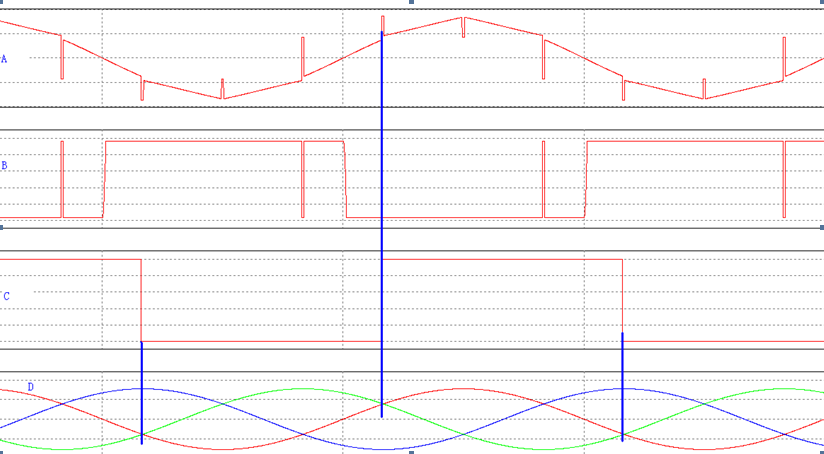

图3、过零脉冲的获取

图4、6路同步信号的获取电路

通过6个光耦就可对称地获取三相的同步信号,这6个同步信号先进行整形,然后进入CPLD进行窄脉冲的去除,在去除窄脉冲时,可以考虑利用延时的方法,延时时间选择为1.66667mS(对应50HZ时的30度),这样既去除了窄脉冲又得到了线电压的过零点信号,然后对这6个信号进行逻辑运算就可得到驱动6个IGBT的信号,完成同步信号的获取。

4、电路的优化

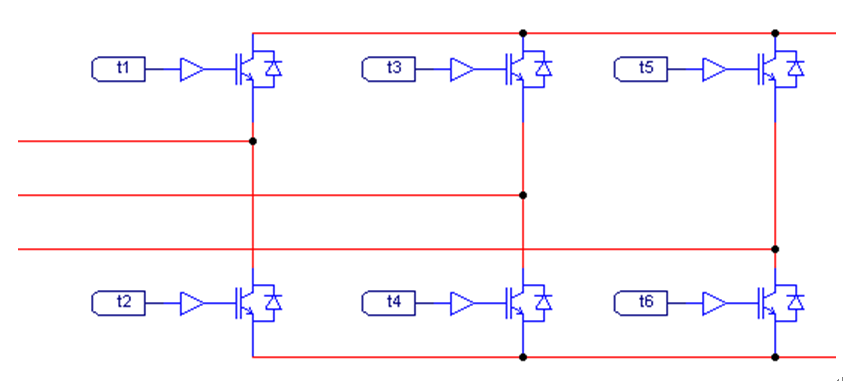

图5、推挽输出的电路

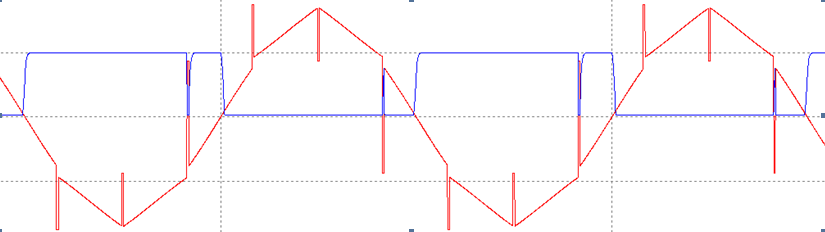

图6、电路的信号波形

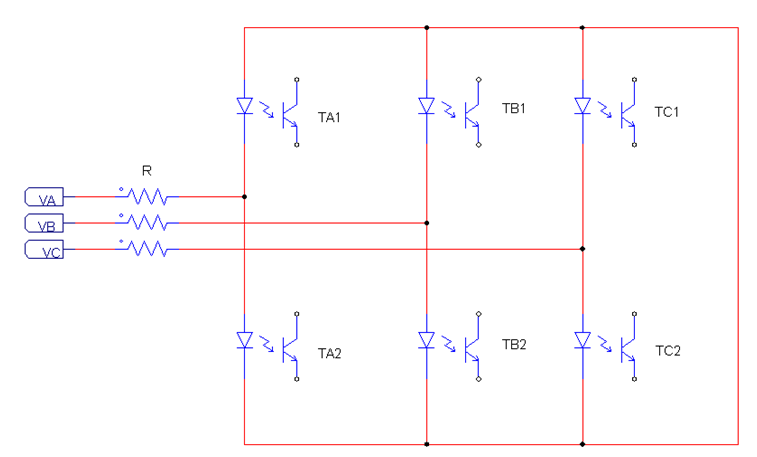

图7、信号的逻辑处理电路

图中t1\t2对应A相,t3\t4对应B相,t5\t6对应C相,假设信号a\b\c进行滤波延时处理后的信号为A\B\C,则6个驱动信号的逻辑处理为:

t1 = A and !B t2 = !A and B

t3 = B and !C t4 = !B and C

t5

= C and !A t6 = !C and

A

这样逻辑处理后正好对应6个IGBT是进行120度工作,在实际中CPLD内还需要对输入的三个信号进行相序的辨识,上面的逻辑关系是对于正序A-B-C的关系,如果是负序(A-C-B)时,需要对逻辑关系进行适当调整,负序时只需要将用到B相的信号与C相进行交换即可。

5、注意的问题

在信号滤波延时过程中需要注意事项,由于光耦前级限流电阻不能选择太小(电阻功率受限),由于电阻值比较大,在光耦次级产生的信号a\b\c存在延时问题,电阻越大延时就越大,此时在滤波延时的时间就要小于1.66667mS,如果不减小延时时间,在回馈电流上就会产生比较大的峰值电流,通过仿真可以看到,如果R=500K时,可以用滤波延时1.2mS时,峰值电流就比较小,如果还用1.66667mS作为滤波延时时,峰值电流能达到正常电流的2倍以上。

在采用这种方法时利用电流触发光耦导通,从而可以提高抗干扰,也不需要做AD变换来进行数字处理,在单元输入缺相时,其光耦产生的信号就不是180度导通的状态,这样就可利用CPLD进行一个逻辑判断就可知道是否缺相。

6、总结